Finite state machine is a graphical model/representation of sequential activities or events. After representing and modeling the events they can be implemented easily in case of sequential logic designs. Finite state machines can be utilized in many fields of study e.g neural networks, artificial intelligence, mathematics, games, robotics and sequential flow of data. Since we are dealing with the sequential circuits so i will explain their use in sequential circuit design in this tutorial. |

- Melay Machine

- Moore Machine

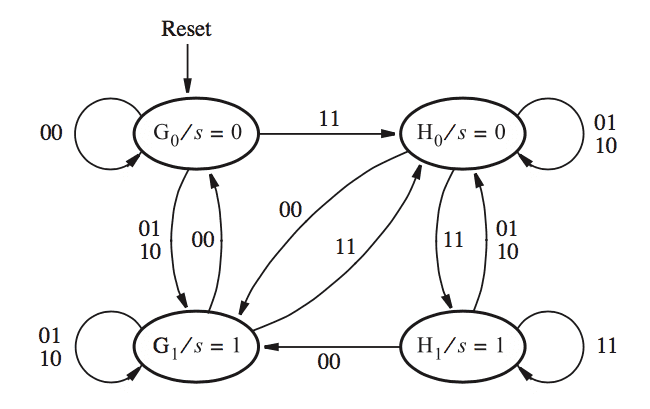

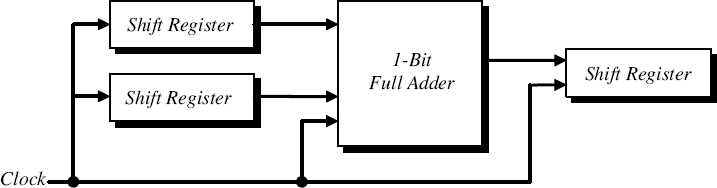

State diagram for serial adder: Let S0 and S1 are the states where the carry in values is '0' and '1' respectively. Figure shows the suitable state diagram defined as a mealy model. The output value sum depends on both state and the present value of the inputs a and b, each transition is labeled using the notation ab / sum which indicates the. Register the block diagram is attached, vhdl code for serial adder using moore type fsm serial adder verilog 4 bit serial adder when doing digital system design it is very common to begin by defining how the system works with a finite state machine model this design step allows the designer to think. Keywords— D-latch, Finite state machine, Mealy Model, Multisim, Serial adder. INTRODUCTION TO FINITE STATE MACHINE Based on the state table we can construct the state diagram. The state diagram is as shown in Fig 2. As observed in the state A finite state machine can be represented by a state transition table or a state diagram. Assume that i want to add 4 signals a,b,c,d and i want to add them using adder2 which adds to signals only.and i want to implement them in adder tree format so in the first state a, and b will be added and saved at signal y and c and d will be added as well and saved at signal z then in the next state y and z will be added and and the result will be at the the output x.

Vhdl Code For Serial Adder Using Finite State Machine

Moore Machine- More number of states in moore compared to melay for same fsm.

- States changes after 1 clock cycle. Latency = 1.

- Synchronous output. Because the states are determined in a process.

- States are output.

Mealy Machine

Vhdl Code For Serial Adder Using Finite State Machine Learning

- Less number of states in mealy compared to moore for same fsm.

- State transition on the same clock cycle. Latency = 0.

- Asynchronous output.

- Transition are output.

Serial Adder Circuit